```

et Run your Neurons

r_pedge = Apedges |- Linder

vec = r pourrentvertbase

posa tren

s = DotFroduct (vec ta-texin)

s /= fa-)texinfu-)texture- wall

```

# Introduction to Microcontrollers

Architecture, Programming, and Interfacing for the Motorola 68HC12

# G. Jack Lipovski

INCLUDED ON CD-ROM

### Introduction to Microcontrollers Architecture, Programming, and Interfacing of the Motorola 68HC12

#### **Academic Press Series in Engineering**

Series Editor

J. David Irwin

Auburn University

Designed to bring together interdependent topics in electrical engineering, mechanical engineering, computer engineering, and manufacturing, the Academic Press Series in Engineering provides state-of-the-art handbooks, textbooks, and professional reference books for researchers, students, and engineers. This series provides readers with a comprehensive group of books essential for success in modern industry. A particular emphasis is given to the applications of cutting-edge research. Engineers, researchers, and students alike will find the Academic Press Series in Engineering to be an indispensable part of their design toolkit.

#### Published books in the series:

Industrial Controls and Manufacturing, 1999, E. Kamen

DSP Integrated Circuits, 1999, L. Wanhammar

Time Domain Electromagnetics, 1999, S. M. Rao

Single- and Multi-Chip Microcontroller Interfacing for the Motorola 68HC12, 1999,

G. J. Lipovski

Control in Robotics and Automation, 1999, B. K. Ghosh, N. Xi, T. J. Tarn Soft Computing and Intelligent Systems, 1999, N. K. Sinha, M. M. Gupta

# Introduction to Microcontrollers

# Architecture, Programming, and Interfacing of the Motorola 68HC12

#### G. Jack Lipovski

Department of Electrical and Computer Engineering University of Texas Austin, Texas

### **ACADEMIC PRESS**

A Harcourt Science and Technology Company

San Diego London Boston New York Sydney Tokyo Toronto

#### Disclaimer:

This eBook does not include the ancillary media that was packaged with the original printed version of the book.

This book is printed on acid-free paper. ⊗

Copyright © 1999 by Academic Press

All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopy, recording, or any information storage and retrieval system, without permission in writing from the publisher.

Academic Press

A Harcourt Science and Technology Company

525 B. St., Suite 1900, San Diego, California 92101-4495, USA http://www.apnet.com

Academic Press 24–28 Oval Road, London NW1 7DX, UK http://www.hbuk.co.uk/ap/

Library of Congress Catalog Card Number: 99-65099

ISBN: 0-12-451831-1

Printed in the United States of America

99 00 01 02 03 DS 9 8 7 6 5 4 3 2 1

### Dedicated to my father, Joseph Lipovski

#### LIMITED WARRANTY AND DISCLAIMER OF LIABILITY

ACADEMIC PRESS ("AP") AND ANYONE ELSE WHO HAS BEEN INVOLVED IN THE CREATION OR PRODUCTION OF THE ACCOMPANYING CODE ("THE PRODUCT") CANNOT AND DO NOT WARRANT THE PERFORMANCE OR RESULTS THAT MAY BE OBTAINED BY USING THE PRODUCT. THE PRODUCT IS SOLD "AS IS" WITHOUT WARRANTY OF ANY KIND (EXCEPT AS HEREAFTER DESCRIBED), EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, ANY WARRANTY OF PERFORMANCE OR ANY IMPLIED WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. AP WARRANTS ONLY THAT THE MAGNETIC DISK(S) ON WHICH THE CODE IS RECORDED IS FREE FROM DEFECTS IN MATERIAL AND FAULTY WORKMANSHIP UNDER THE NORMAL USE AND SERVICE FOR A PERIOD OF NINETY (90) DAYS FROM THE DATE THE PRODUCT IS DELIVERED. THE PURCHASER'S SOLE AND EXCLUSIVE REMEDY IN THE EVENT OF A DEFECT IS EXPRESSLY LIMITED TO EITHER REPLACEMENT OF THE DISK(S) OR REFUND OF THE PURCHASE PRICE, AT AP'S SOLE DISCRETION.

IN NO EVENT, WHETHER AS A RESULT OF BREACH OF CONTRACT, WARRANTY OR TORT (INCLUDING NEGLIGENCE), WILL AP OR ANYONE WHO HAS BEEN INVOLVED IN THE CREATION OR PRODUCTION OF THE PRODUCT BE LIABLE TO PURCHASER FOR ANY DAMAGES, INCLUDING ANY LOST PROFITS, LOST SAVINGS OR OTHER INCIDENTAL OR CONSEQUENTIAL DAMAGES ARISING OUT OF THE USE OR INABILITY TO USE THE PRODUCT OR ANY MODIFICATIONS THEREOF, OR DUE TO THE CONTENTS OF THE CODE, EVEN IF AP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. OR FOR ANY CLAIM BY ANY OTHER PARTY.

ANY REQUEST FOR REPLACEMENT OF A DEFECTIVE DISK MUST BE POSTAGE PREPAID AND MUST BE ACCOMPANIED BY THE ORIGINAL DEFECTIVE DISK, YOUR MAILING ADDRESS AND TELEPHONE NUMBER, AND PROOF OF DATE OF PURCHASE AND PURCHASE PRICE. SEND SUCH REQUESTS, STATING THE NATURE OF THE PROBLEM, TO ACADEMIC PRESS CUSTOMER SERVICE, 6277 SEA HARBOR DRIVE, ORLANDO, FL 32887, 1-800-321-5068. AP SHALL HAVE NO OBLIGATION TO REFUND THE PURCHASE PRICE OR TO REPLACE A DISK BASED ON CLAIMS OF DEFECTS IN THE NATURE OR OPERATION OF THE PRODUCT.

SOME STATES DO NOT ALLOW LIMITATION ON HOW LONG AN IMPLIED WARRANTY LASTS, NOR EXCLUSIONS OR LIMITATIONS OF INCIDENTAL OR CONSEQUENTIAL DAMAGE, SO THE ABOVE LIMITATIONS AND EXCLUSIONS MAY NOT APPLY TO YOU. THIS WARRANTY GIVES YOU SPECIFIC LEGAL RIGHTS, AND YOU MAY ALSO HAVE OTHER RIGHTS WHICH VARY FROM JURISDICTION TO JURISDICTION.

THE RE-EXPORT OF UNITED STATES ORIGIN SOFTWARE IS SUBJECT TO THE UNITED STATES LAWS UNDER THE EXPORT ADMINISTRATION ACT OF 1969 AS AMENDED. ANY FURTHER SALE OF THE PRODUCT SHALL BE IN COMPLIANCE WITH THE UNITED STATES DEPARTMENT OF COMMERCE ADMINISTRATION REGULATIONS. COMPLIANCE WITH SUCH REGULATIONS IS YOUR RESPONSIBILITY AND NOT THE RESPONSIBILITY OF AP.

# **Contents**

| Pre  | face                                              | X I |  |  |

|------|---------------------------------------------------|-----|--|--|

| List | st of Figures                                     |     |  |  |

| List | st of Tables                                      |     |  |  |

| Acl  | knowledgments                                     | xxi |  |  |

| Abo  | About the Author                                  |     |  |  |

| 1    | Basic Computer Structure and the 6812             | 1   |  |  |

| 1.1  | Basic Computer Structure                          | 1   |  |  |

| 1.2  | The Instruction                                   | 4   |  |  |

| 1.3  | A Few Instructions and Some Simple Programs       | 8   |  |  |

| 1.4  | MC68HC812A4 and MC68HC912B32 Organizations        | 16  |  |  |

| 1.5  | Variable Word Width                               | 19  |  |  |

| 1.6  | Summary and Further Reading                       | 21  |  |  |

|      | Problems                                          | 23  |  |  |

| 2    | The Instruction Set                               | 27  |  |  |

| 2.1  | Move Instructions                                 | 28  |  |  |

| 2.2  | Arithmetic Instructions                           | 34  |  |  |

| 2.3  | Logic Instructions                                | 38  |  |  |

| 2.4  | Edit Instructions                                 | 41  |  |  |

| 2.5  | Control instructions                              | 42  |  |  |

| 2.6  | Input-Output Instructions                         | 49  |  |  |

| 2.7  | Special Instructions                              | 49  |  |  |

| 2.8  | Remarks                                           | 51  |  |  |

|      | Problems                                          | 53  |  |  |

| 3    | Addressing                                        | 57  |  |  |

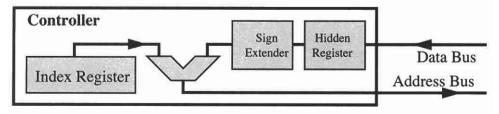

| 3.1  | Op Code Byte Addressing Modes                     | 58  |  |  |

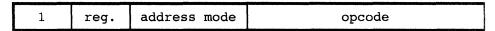

| 3.2  | Post-Byte Index Addressing Modes                  | 60  |  |  |

| 3.3  | Relative Addressing and Position Independence     | 67  |  |  |

| 3.4  | Stack Index Addressing, Reentrancy, and Recursion | 71  |  |  |

| 3.5  | Examples                                          | 76  |  |  |

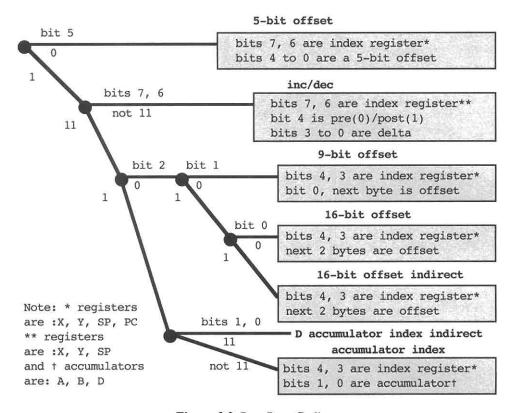

| 3.6  | Architectural Notions of Addressing               | 78  |  |  |

| - CD 1 | 1  | c  | ~   |      | 2    |

|--------|----|----|-----|------|------|

| lar    | NΑ | ΛŤ | Cor | TART | t c' |

|        |    |    |     |      |      |

| 3.7 | Summary                                         | 81         |

|-----|-------------------------------------------------|------------|

|     | Problems                                        | 82         |

| 4   | Assembly Language Programming                   | 87         |

| 4.1 | Introductory Example and Assembler Printout     | 89         |

| 4.2 | Assembler Directives                            | 92         |

| 4.3 | Mechanics of a Two-Pass Assembler               | 96         |

| 4.4 | Character String Operations                     | 99         |

| 4.5 | A Simplified Two-Pass Assembler                 | 103        |

| 4.6 | Summary<br>Problems                             | 107<br>109 |

| 5   | Advanced Assemblers, Linkers, and Loaders       | 119        |

| 5.1 | Cross Assemblers and Downloaders                | 119        |

| 5.2 | Relocatable Assemblers and Loaders              | 123        |

| 5.3 | Conditional Assemblers                          | 125        |

| 5.4 | Macro Assemblers                                | 127        |

| 5.5 | Documentation                                   | 130        |

| 5.6 | Summary                                         | 132        |

|     | Problems                                        | 133        |

| 6   | Assembler Language Subroutines                  | 137        |

| 6.1 | Local Variables                                 | 139        |

| 6.2 | Passing Parameters                              | 149        |

| 6.3 | Passing Arguments by Value, Reference, and Name | 162        |

| 6.4 | Calling and Returning Mechanisms                | 163        |

| 6.5 | Summary                                         | 172        |

|     | Problems                                        | 173        |

| 7   | Arithmetic Operations                           | 179        |

| 7.1 | Multiplication and Division                     | 180        |

| 7.2 | Integer Conversion                              | 183        |

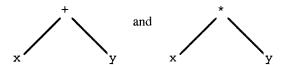

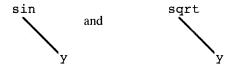

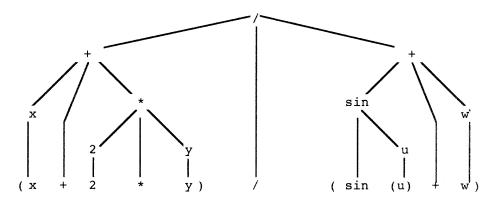

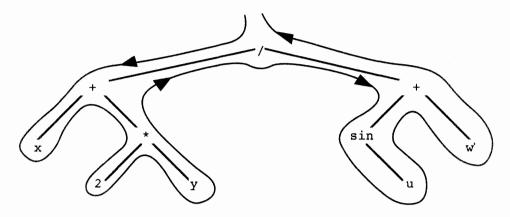

| 7.3 | From Formulas to Subroutine Calls               | 191        |

| 7.4 | Long Integer Arithmetic                         | 196        |

| 7.5 | Floating-Point Arithmetic and Conversion        | 201        |

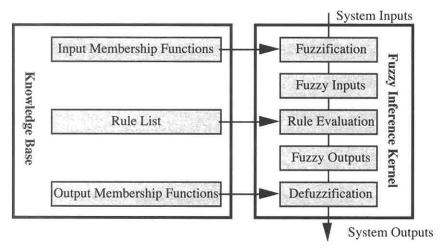

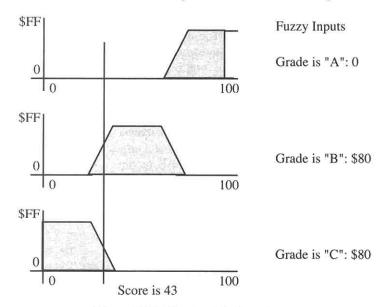

| 7.6 | Fuzzy Logic                                     | 210        |

| 7.7 | Summary<br>Problems                             | 215<br>217 |

| 8   | Programming in C and C++                        | 221        |

|     |                                                 |            |

| 8.1 | Compilers and Interpreters                      | 221        |

| 8.2 | Operators and Assignment Statements             | 223        |

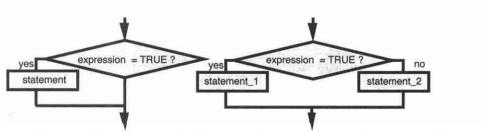

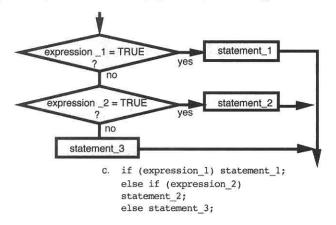

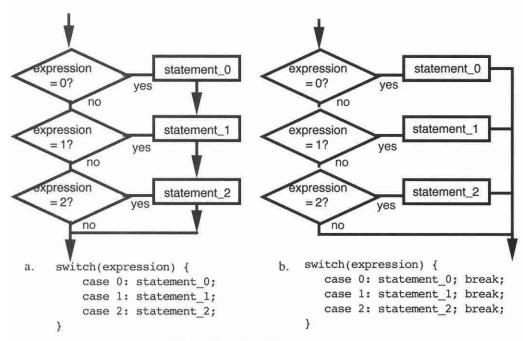

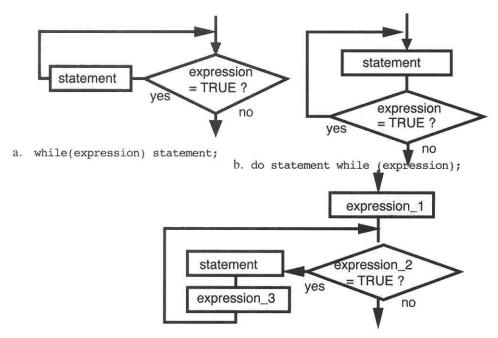

| 8.3 | Conditional and Loop Statements                 | 226        |

TEAM LRN

| Tabl                                                 | e of Contents                                                                                                                                                                                                                                     | ix                                                                 |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 8.4<br>8.5<br>8.6<br>8.7<br>8.8                      | Constants and Variables Procedures and Their Arguments An Example Object-Oriented Programming in C++ Summary Problems                                                                                                                             | 227<br>231<br>233<br>236<br>245<br>246                             |

| 9                                                    | Implementation of C Procedures                                                                                                                                                                                                                    | 253                                                                |

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7        | Global and Local Variables Expressions and Assignment Statements Conditional Statements Loop Statements, Arrays, and Structs Procedure Calls and Arguments Examples from Character String Procedures Summary Problems                             | 254<br>257<br>265<br>274<br>279<br>282<br>286<br>287               |

| 10                                                   | Elementary Data Structures                                                                                                                                                                                                                        | 291                                                                |

| 10.2<br>10.3<br>10.4                                 | What a Data Structure Is Indexable Data Structures Sequential Data Structures Linked List Structures Summary Problems                                                                                                                             | 291<br>293<br>298<br>304<br>310<br>311                             |

| 11                                                   | Input/Output                                                                                                                                                                                                                                      | 317                                                                |

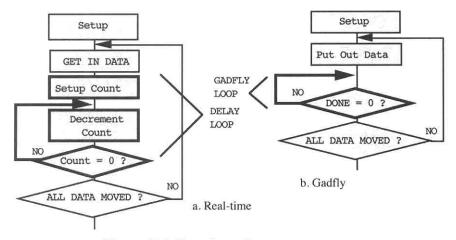

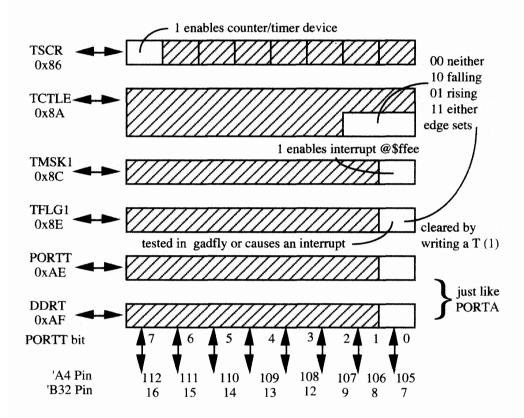

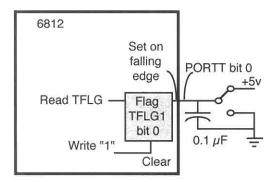

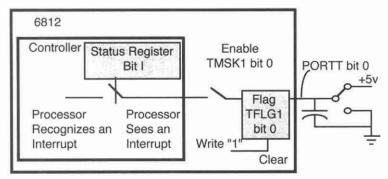

| 11.2<br>11.3<br>11.4<br>11.5<br>11.6<br>11.7<br>11.8 | Input and Output Devices Parallel Ports Input and Output Software Synchronization Hardware Gadfly Synchronization Interrupt Synchronization Analog-to-Digital and Digital-to-Analog Conversion UART Protocol Summary and Further Reading Problems | 317<br>320<br>322<br>325<br>326<br>329<br>334<br>337<br>340<br>341 |

| 12                                                   | Other Microcontrollers                                                                                                                                                                                                                            | 349                                                                |

| 12.2<br>12.3<br>12.4                                 | The 6811 The 6808 The 6805 The 68300 Series The 500 Series                                                                                                                                                                                        | 349<br>352<br>356<br>358<br>367                                    |

| X    |          |                                                 | Table of Contents |

|------|----------|-------------------------------------------------|-------------------|

|      |          | ·CORE Series                                    | 370               |

|      |          | ng a Microcontroller for an Application         | 374               |

| 12.8 | Summa    | •                                               | 375               |

|      | Proble   | nis                                             | 377               |

| App  | endice   | s                                               |                   |

| Appe | endix 1: | Number Representations and Binary Arithmetic    | 381               |

|      | A1.1     | Number Representations                          | 381               |

|      | A1.2     | Binary Arithmetic                               | 382               |

|      | A1.3     | Remarks                                         | 385               |

|      |          | Problems                                        | 386               |

| Appe | endix 2: | Using HiWare CD-ROM                             | 387               |

|      | A2.1     | Loading HiWare Software                         | 387               |

|      | A2.2     | Opening the HiWare Toolbox                      | 387               |

|      | A2.3     | Running Examples From the ManualProgramFolder   | 387               |

|      | A2.4     | Running Examples From the AssemblyProgramFolder | 388               |

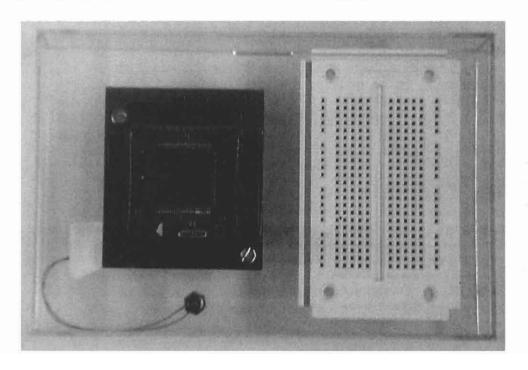

|      | A2.5     | Downloading to a 'B32 Board                     | 389               |

|      | A2.6     | POD-Mode BDM Interface                          | 389               |

|      | A2.7     | Techniques for HiWare Tools                     | 390               |

|      |          |                                                 |                   |

391

Index

Preface xi

#### PREFACE

Programming is an essential engineering skill. To almost any engineer, it is as important as circuit design to an electrical engineer, as statistics to a civil engineer, and as heat transfer to a chemical engineer. The engineer has to program in high-level languages to solve problems. He or she also should be able to read assembly-language programs to understand what a high-level language does. Finally, he or she should understand the capabilities of a microcontroller because they are components in many systems designed, marketed, and maintained by engineers. The first goal of this book then is to teach engineers how a computer executes instructions. The second goal is to teach the engineer how a high-level language statement converts to assembler language. A final goal is to teach the engineer what can be done on a small computer and how the microcomputer is interfaced to the outside world. Even the nonprogramming engineer should understand these issues. Although this book is written for engineers, it will serve equally well for anyone, even hobbyists, interested in these goals.

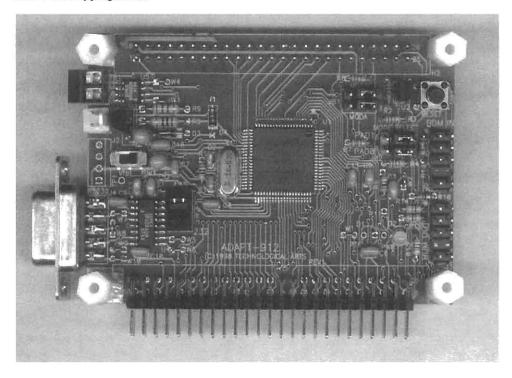

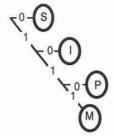

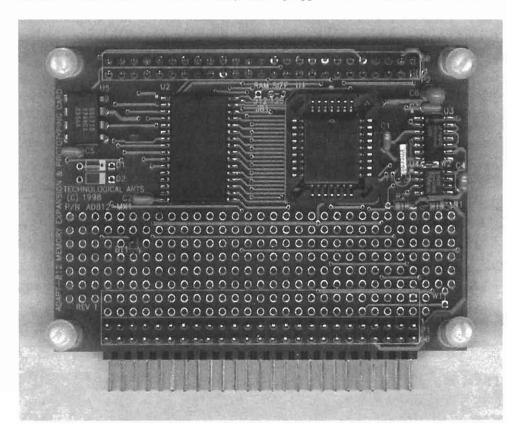

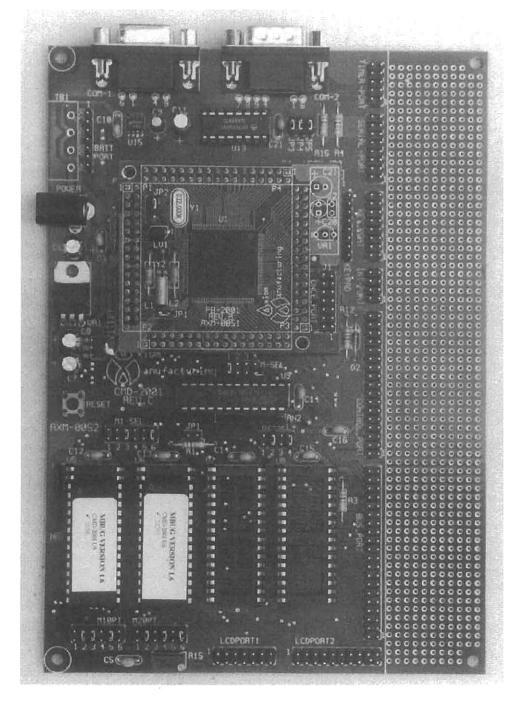

The reader is taught the principles of assembly-language programming by being shown how to program a particular microcomputer, the Motorola 6812. The important thing about the 6812 is that it has a straightforward yet powerful instruction set, midway between smaller and more powerful microcontrollers; from it the reader can adjust to these smaller or more powerful microcontrollers. The best way to learn these principles is to write a lot of programs, debug them, and see them work on a real microcontroller. This hands-on experience can be inexpensively obtained on the 6812. Several 6812 boards, which do everything described in this book, are available for under \$100. (This price doesn't include the personal computer that hosts the 6812 target system.)

The following discussion outlines the book and explains several decisions that were made when we wrote the book. Optional chapters are available for readers having various interests. The main skills taught in each chapter are summarized.

Chapters 1 to 3 discuss programming using hand-translated machine code, and the implementation of machine instructions in an idealized microcontroller. The assembler is not introduced until Chapter 4. This gives the engineering student a fine feeling for the machine and how it works, and helps him or her resolve problems encountered later with timing in input/output programming or with the use of addressing modes in managing data structures. Chapter 1 explains how a microprocessor interacts with the memory and how it executes the instruction cycle. The explanation focuses on a microcomputer and is simplified to provide just enough background for the remainder of the text. Simple instructions and elementary programs are introduced next. Pointing out that there is no best program to solve a problem, Chapter 1 observes what makes a good program and encourages the reader to appreciate good programming style. A discussion of the available organizations of 6812 microcontrollers concludes this chapter.

In Chapter 2, the main concept is the alternative forms of the same kind of instruction on the 6812. Rather than listing the instructions alphabetically, as is desirable in a reference book, we group together instructions that perform the same type of function. Our groups are the classical ones, namely, the move, arithmetic, logical, edit, control, and input/output groups. Although other groupings are also useful, this one seems to encourage the student to try alternative instructions as a way of looking for the best instruction for his or her purpose. The 6812 has an extensive set of addressing modes that can be used with most instructions; these are covered in Chapter 3. The

xii Preface

different addressing modes are introduced with a goal of explaining why these modes are useful as well as how they work. Examples at the end of the chapter illustrate the use of these modes with the instructions introduced in Chapter 2.

The end of Chapter 3 shows the use of program-relative addressing for position independence and the use of stack addressing for recursion and reentrancy.

Chapters 4 to 6 show how a program can be more easily written in assembler and the high-level C language and translated into machine code by an assembler. Chapter 4 introduces the assembler, explains assembler directives and symbolic addresses, and introduces limitations of forward referencing in a two-pass assembler. Assembly language examples that build on the examples from previous chapters conclude Chapter 4. Chapter 5, which may be omitted if the reader is not going to write assembler language programs, provides insights needed by programmers who write large assembler language programs. A general discussion of related programs, including macro, conditional, and relocatable assemblers and linkers, is given.

Chapter 6 develops assembler language subroutines. It illustrates techniques used in assembler language at an implementation level (such as passing arguments in registers). The tradeoffs between macros and subroutines as a means to insert the same program segment into different places in a program are discussed.

Chapter 7 covers arithmetic routines. An implementation is shown for unsigned and signed multiplication and division. Conversion between different bases is discussed and examples are given illustrating conversion from ASCII decimal to binary and vice versa. Stack operation and Polish notation are shown to be useful in realizing arithmetic routines of any complexity. Multiple-precision integer arithmetic is discussed by means of examples of 32-bit operations including multiplication and division. Floating-point representations are introduced, and the mechanics of common floating- point operations are discussed. Finally, a 6812-oriented introduction of fuzzy logic is presented.

Chapter 8, which may be omitted if the reader is already familiar with C, discusses compilers and interpreters, and briefly introduces C programming to provide a background for later chapters.

Chapter 9 introduces the implementation of C procedures. Several constructs in C, such as switch statements, are shown implemented in assembler language. The techniques C uses to hold local variables and to pass arguments to a subroutine on the stack are shown implemented in assembler language.

Chapter 10 covers elementary data structures. The simplest, including the character string used in earlier chapters, and the more involved deque and linked list structures are related to the addressing modes available in the 6812. The main theme of this chapter is that the correct storage of data can significantly improve the efficiency of a program.

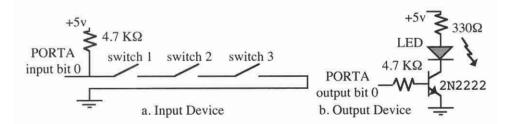

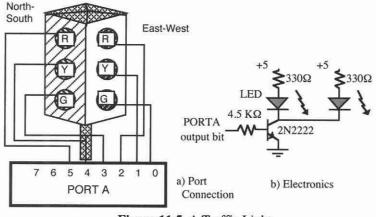

Chapter 11 introduces input/output programming. Input and output devices are characterized. Then the 6812's parallel ports are described. Input and output software is illustrated with some examples. We then show 6812 synchronization hardware, to introduce gadfly and interrupt synchronization. Finally we show how D-to-A and A-to-D conversion is done.

Chapter 12 shows how the assembly language of a different microcontroller might be learned once that of the 6812 has been learned. Although we would like to discuss other popular microcontrollers, we believe that we could fill another book doing that. To illustrate the idea, we look at the near relatives less costly than the 6812, in particular, the 6805, 6808, and 6811. We also discuss briefly more powerful microcontrollers such

Preface xiii

as the 68300, 500, and M CORE series. The main theme is that once you understand the instruction set of one microcontroller, you can quickly learn to program efficiently on other microcontrollers.

This book systematically develops the concepts of programming of a microcontroller in high-level language and assembly language. It also covers the principles of good programming practice through top-down design and the use of data structures. It is suitable as an introductory text for a core course in an engineering curriculum on assembly language programming or as the first course on microcomputers that demonstrates what a small computer can do. It may also be used by those who want to delve more deeply into assembly language principles and practices. You should find, as we have, that programming is a skill that magnifies the knowledge and control of the programmer, and you should find that programming, though very much an important engineering skill, is fun and challenging. This book is dedicated to show you that.

Problems are a major part of a good textbook. We have developed over twenty problems for each chapter, and for each section we generally have at least two problems, one that can be assigned for homework, while the other can be used in a quiz or exam. Some of these problems are "brain teasers" that are designed to teach the student that even simple programs should be tested, generally at their extreme values, to be sure they work. Often the obvious and simple solutions succumb to truncation or overflow errors. Also, problems in Chapter 11, including the keyless entry design and the experiment that plays "The Eyes of Texas" on a pair of earphones, are absolutely great motivators for sophomores, when they get them to work on a real microcontroller board. They see how exciting computer engineering is. This is having a significant impact on retention. An instructor's manual, available from the publisher, includes solutions to all the problems given at the end of each chapter.

This book was developed largely from a book by the author and T. J. Wagner on the 6809. The author expresses his gratitude for the contributions made by Dr. Wagner through his writing of much of the earlier book.

xiv List of Figures

# **List of Figures**

| Figure      | Title                                                       | Page |

|-------------|-------------------------------------------------------------|------|

| Figure 1.1  | Simplified Computer Structure                               | 2    |

| Figure 1.2  | Registers in the 6812                                       | 5    |

| Figure 1.3  | Registers and Memory                                        | 9    |

| Figure 1.4  | Data Operator Arithmetic                                    | 11   |

| Figure 1.5  | Program for 8-Bit Addition                                  | 11   |

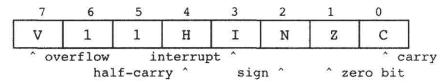

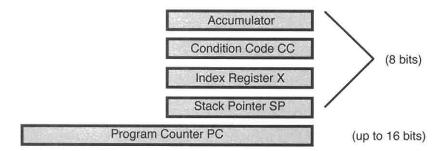

| Figure 1.6  | Bits in the Condition Code Register                         | 12   |

| Figure 1.7  | Addition of Two-Byte Numbers                                | 12   |

| Figure 1.8  | Program for 16-Bit Addition                                 | 13   |

| Figure 1.9  | Alternative Program for 16-Bit Addition                     | 13   |

| Figure 1.10 | Most Efficient Program for 16-Bit Addition                  | 15   |

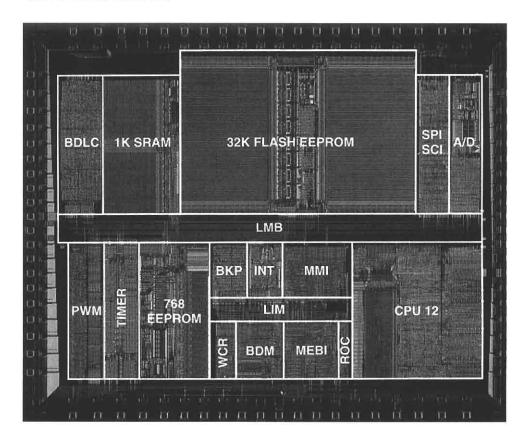

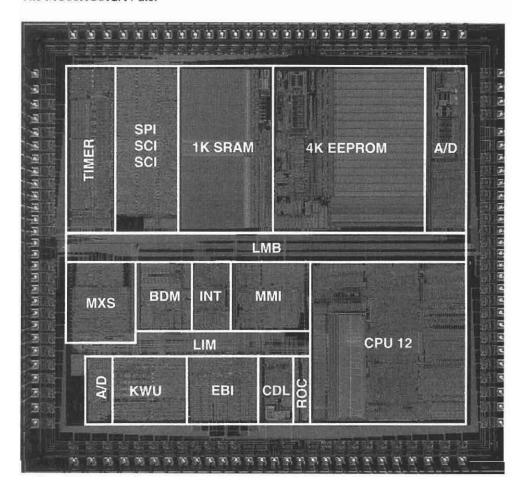

| Figure 1.11 | Single-Chip Mode of the MC68HC812A4                         | 16   |

| Figure 1.12 | Expanded Wide Multiplexed Bus Mode of the MC68HC812A4       | 17   |

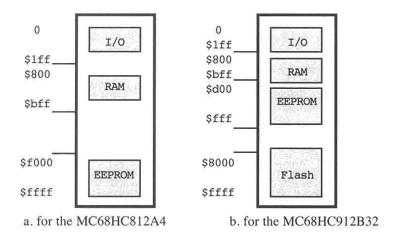

| Figure 1.13 | Memory Maps for the 6812                                    | 17   |

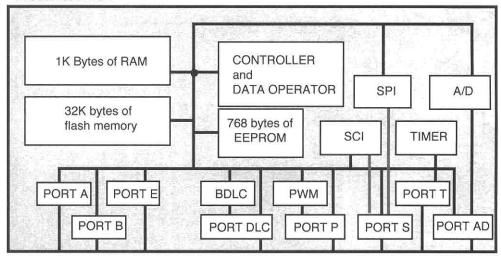

|             | Single-Chip Mode of the MC68HC912B32                        | 18   |

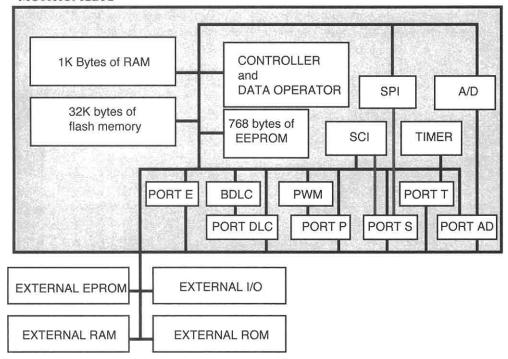

| Figure 1.15 | Expanded Wide Multiplexed Bus Mode of the MC68HC912B32      | 19   |

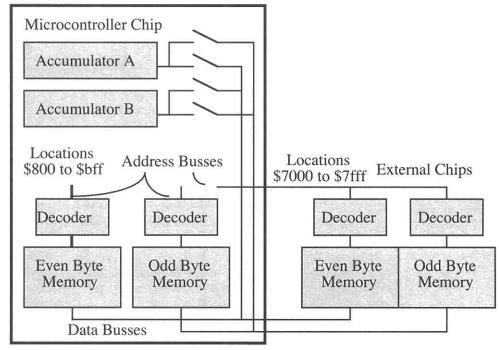

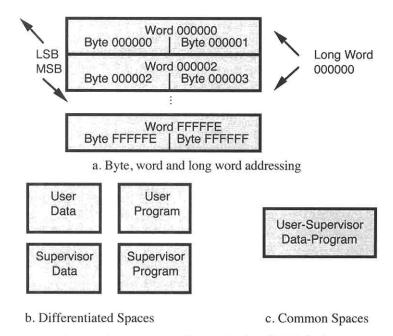

| Figure 1.16 | Variable Word Width Implementation                          | 20   |

| Figure 2.1  | A Program Segment to Clear a Byte                           | 28   |

| Figure 2.2  | A Stack                                                     | 30   |

| Figure 2.3  | Transfers between Registers                                 | 32   |

| Figure 2.4  | Program Segment to Initialize the Condition Code Register   | 33   |

| Figure 2.5  | Program Segment for 32-Bit Addition                         | 35   |

| Figure 2.6  | Multiplication                                              | 36   |

| Figure 2.7  | Program Segment for 16-Bit Unsigned Multiplication          | 36   |

| Figure 2.8  | Program Segment for BCD Addition                            | 37   |

| Figure 2.9  | Program Segment for Conversion from Celsius to Fahrenheit   | 37   |

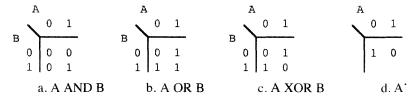

| Figure 2.10 | Common Logic Operations                                     | 38   |

| Figure 2.11 | Bit-by-Bit AND                                              | 39   |

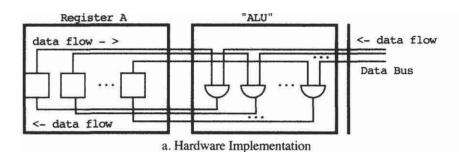

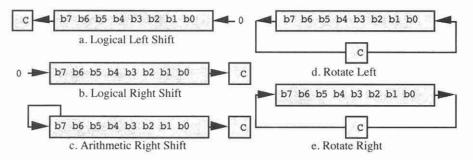

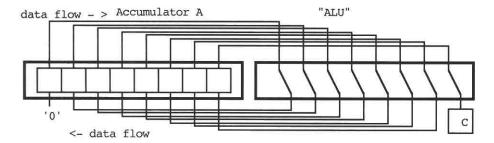

| Figure 2.12 | Shifts and Rotates                                          | 40   |

| Figure 2.13 | Shift Hardware                                              | 41   |

| Figure 2.14 | Program Segment to Swap Nibbles                             | 41   |

| Figure 2.15 | Program Segment for Insertion of Some Bits                  | 42   |

| Figure 2.16 | Decision Tree                                               | 44   |

| Figure 2.17 | Program Segment for a Decision Tree                         | 44   |

| Figure 2.18 | Program Segment for Setting, Clearing, and Testing of a Bit | 45   |

| Figure 2.19 | Program Segment for a Wait Loop                             | 46   |

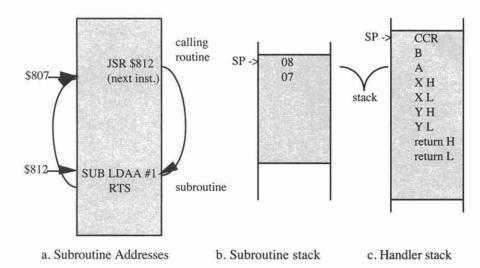

|             | Subroutine and Handler Addresses                            | 47   |

| Figure 2.21 | Program Segment for Swap Subroutine                         | 47   |

| Figure 2.22 | Program Segment for Ensuring a Value Is between Limits      | 50   |

| Figure 2.23 | Program Segment for a Multiply and Add Operation            | 51   |

| List of Figures | ιv |

|-----------------|----|

| Figure 3.1  | Op Code Byte Coding                                           | 60   |

|-------------|---------------------------------------------------------------|------|

| Figure 3.2  | Post Byte Coding                                              | 62   |

| Figure 3.3  | Program segment to Add Two Bytes Using Vector Indexing        | 63   |

| Figure 3.4  | Offset Calculation                                            | 63   |

| Figure 3.5  | Autoincrement Address Calculation                             | 64   |

| Figure 3.6  | Program segment to Add Two Bytes Using Autoincrementing       | 65   |

| Figure 3.7  | Accumulator Index Address Calculation                         | 66   |

| Figure 3.8  | Simplified Control Hardware for Relative Addressing           | 68   |

| Figure 3.9  | Program Segment Using BRA, Illustrating Position Independence | 69   |

| Figure 3.10 | Program Segment to Put a Square Wave on an Output Port        | 69   |

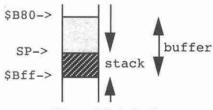

| Figure 3.11 | A Stack Buffer for Two Stacks                                 | 72   |

| Figure 3.12 | Subroutine to Compute n! Recursively                          | 73   |

| Figure 3.13 | Subroutine to Compute n! in a Loop                            | 73   |

| Figure 3.14 | Nonreentrant Subroutine to Delay                              | 74   |

| Figure 3.15 | Reentrant Subroutine to Ckear Memory                          | 74   |

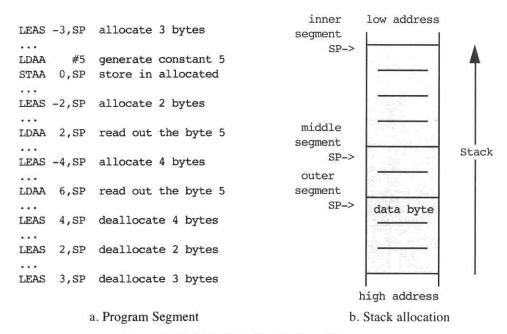

| Figure 3.16 | A Stack Buffer for Nested Segments                            | 75   |

| Figure 3.17 | Program Segment to Clear a Block of Memory                    | 76   |

| Figure 3.18 | Program Segment to Move a Block of Memory                     | 77   |

| Figure 3.19 | Program Segment to Add Vector Elements                        | 77   |

| Figure 3.20 | Program Segment to Compute an Inner Product                   | 78   |

| Figure 3.21 | A Table                                                       | 85   |

|             |                                                               |      |

| Figure 4.1  | Program MAX                                                   | 89   |

| Figure 4.2  | Assembler Source Code for the Program MAX                     | 90   |

| Figure 4.3  | Assembler Listing for the Program MAX                         | 92   |

| Figure 4.4  | Assembler Listing for the Program Square                      | 96   |

| Figure 4.5  | Program to Select Negative Odd Numbers                        | 97   |

| Figure 4.6  | Program with Illegal Forward Reference                        | 98   |

| Figure 4.7  | Program without Forward Reference                             | - 99 |

| Figure 4.8  | Print Program                                                 | 100  |

| Figure 4.9  | Character Move Program Segment and Data                       | 101  |

| Figure 4.10 | Character String Compare Program Segment and Data             | 101  |

| Figure 4.11 | Character Search in a String                                  | 102  |

| Figure 4.12 | Directory Program Segments                                    | 102  |

| Figure 4.13 | Machine and Source Code                                       | 103  |

| Figure 4.14 | Simple Computer and Assembler SA1 Specifications              | 103  |

| Figure 4.15 | Assembler Main Program                                        | 104  |

| Figure 4.16 | Assembler Directives                                          | 104  |

| -           | Assembler Pass 1                                              | 104  |

| _           | Assembler Pass 2                                              | 105  |

| _           | Subroutine to Get the Opcode                                  | 106  |

|             | Subroutine to Insert a Label as an Operand                    | 106  |

|             | Convert ASCII Hex String to a Binary Number                   | 107  |

|             | Program with Relative Address Reference                       | 110  |

|             | Program with Direct or Page Zero Reference                    | 110  |

| Figure 4.24 | •                                                             | 112  |

| Figure 4.25 | Another Program with Errors                                   | 113  |

xvi List of Figures

| Figure 4.26 | Machine and Source Code for SA2                                        | 113 |

|-------------|------------------------------------------------------------------------|-----|

| _           | FINDLBL Subroutine with Errors                                         | 115 |

| Figure 4.28 | Line Print Subroutine with Errors                                      | 116 |

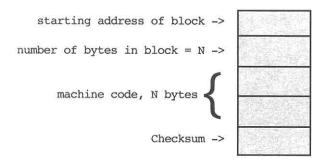

| Figure 5.1  | Loader Record                                                          | 121 |

| Figure 5.2  | An S- Record                                                           | 121 |

| Figure 5.3  | A Program                                                              | 122 |

| Figure 5.4  | Sections in Different Source Code Files                                | 123 |

| Figure 5.5  | A Parameter File                                                       | 124 |

| Figure 5.6  | Loop Macro to Add Consecutive Values                                   | 129 |

| Figure 5.7  | Recursive Macro to Add up to Eight Values                              | 129 |

| Figure 5.8  | Example Control Sequence Program                                       | 131 |

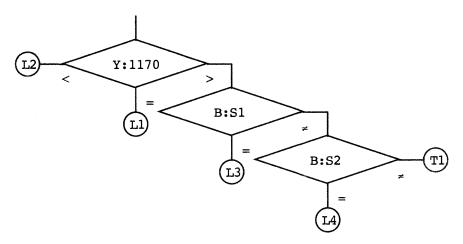

| Figure 5.9  | Flowchart for Example Control Sequence                                 | 132 |

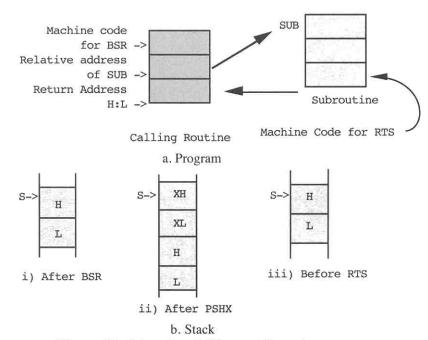

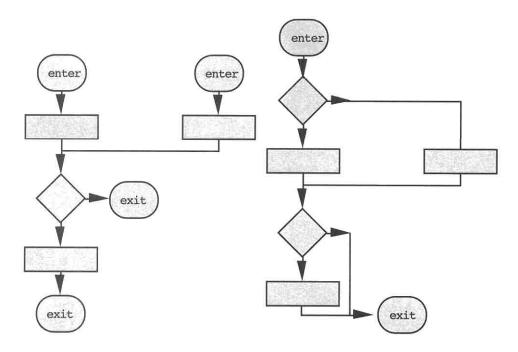

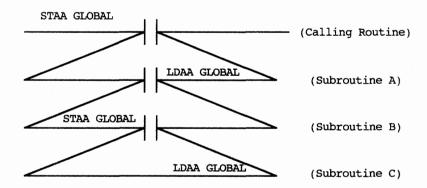

| Figure 6.1  | Subroutine Calling and Returning                                       | 138 |

| Figure 6.2  | Program Segment with a Plurality of Entry and Exit Points              | 139 |

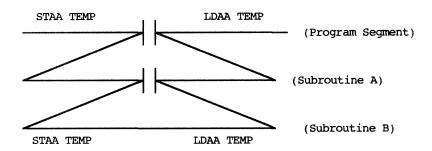

| Figure 6.3  | Changing a Global Variable before It Has Been Completely Used          | 141 |

| Figure 6.4  | Inner Product Utilizing a Global Variable such as TEMP (a Bad Example) | 141 |

| Figure 6.5  | Inner Product Utilizing Different Global Variables (a Bad Example)     | 142 |

| Figure 6.6  | Inner Product Registers                                                | 142 |

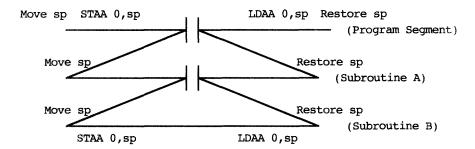

| Figure 6.7  | Inner Product Program Segment Utilizing Local Variables on the Stack   | 143 |

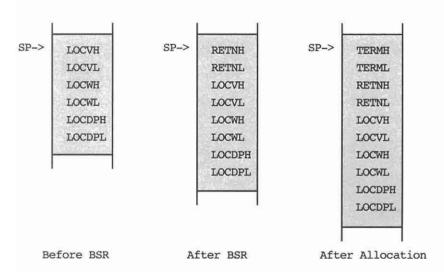

| Figure 6.8  | Nested Subroutines Using Local Variables                               | 144 |

| Figure 6.9  | Local variables stored on the stack, for Successive Subroutines        | 144 |

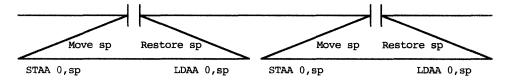

| Figure 6.10 | Using Symbolic Names for Stacked Local Variables                       | 145 |

| Figure 6.11 | Defining Symbolic Names for Stacked Local Variables by Sizes           | 146 |

| Figure 6.12 | Declaring Symbolic Names for Local Variables using DS Directives       | 146 |

| Figure 6.13 | Declaring Symbolic Names for Extended Local Access                     | 147 |

| Figure 6.14 | Accessing Stacked Local Variables Using a Stack Marker                 | 148 |

|             | A Subroutine with Parameters in Registers                              | 150 |

| -           | Change a Global Parameter before its Subroutine Has Used It            | 152 |

| •           | A Subroutine with Parameters in Global Variables                       | 152 |

| -           | Calling a Subroutine for Figure 6.17                                   | 153 |

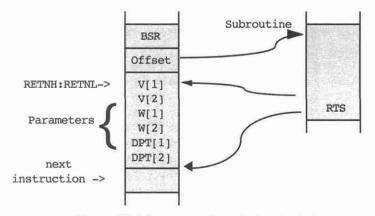

|             | Calling a Subroutine with Parameters on the Stack for Figure 6.21      | 153 |

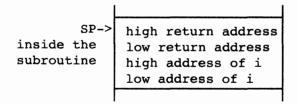

|             | Location of Parameters Passed on the Hardware Stack                    | 154 |

| _           | A Subroutine with Parameters on the Stack                              | 154 |

| -           | Revised Subroutine with Local Variables and Parameters on the Stack    |     |

|             | Calling a Subroutine with Parameters on the Stack for Figure 6.22      | 155 |

| _           | Parameters Passed after the Call                                       | 156 |

| -           | A Subroutine with Parameters after the Call, which Pulls the Return    | 157 |

| -           | A Subroutine Calling Sequence for Figure 6.25                          | 157 |

|             | A Subroutine with Parameters after the Call, Which Uses RTS            | 158 |

| , -         | A Subroutine Call with Parameters after the Call for Figure 6.27       | 158 |

| Figure 6.29 | A Subroutine with In-Line Parameters that Are Addresses                | 159 |

| Figure 6.30 | An In-Line Argument List of Addresses, for Figure 6.29                 | 159 |

| Figure 6.31 | Implementation of a C or C++ switch—Case Statement                     | 160 |

| List of Figur | res                                                            | xvii       |

|---------------|----------------------------------------------------------------|------------|

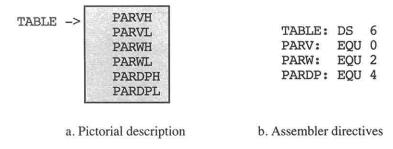

| F: ( 22       | Decrees the second in a Table                                  | 161        |

| _             | Parameters in a Table                                          | 161        |

| Figure 6.33   | • •                                                            | 162        |

| Figure 6.34   | -                                                              | 164        |

| Figure 6.35   | * * *                                                          | 164        |

| Figure 6.36   |                                                                | 165        |

| Figure 6.37   | • •                                                            | 165        |

| Figure 6.38   |                                                                | 166        |

| Figure 6.39   | - · · · · · · · · · · · · · · · · · · ·                        | 167        |

| Figure 6.40   | -                                                              | 167        |

| Figure 6.41   |                                                                | 167        |

| Figure 6.42   |                                                                | 168<br>169 |

| Figure 6.43   |                                                                | 169        |

| Figure 6.44   | •                                                              | 170        |

| Figure 6.45   | A Trap Handler Calling a Trap Handler                          | 170        |

| _             | Program for Problem 13                                         | 175        |

| rigule 0.47   | Flogram for Floorem 15                                         | 175        |

| Figure 7.1    | 8-Bit Unsigned Multiply Subroutine                             | 180        |

| Figure 7.2    | 8-Bit Unsigned Divide Subroutine                               | 181        |

| Figure 7.3    | 8-Bit Signed Multiply Subroutine                               | 183        |

| Figure 7.4    | Conversion from Decimal to Binary Multiplying by Powers of 10  | 185        |

| Figure 7.5    | Conversion from Decimal to Binary by Multiplication by 10      | 186        |

| Figure 7.6    | Conversion from Binary to Decimal by Successive Subtraction    | 187        |

| Figure 7.7    | Conversion from Binary to Decimal by Division by Powers of Ten | 188        |

| Figure 7.8    | Conversion from Binary to Decimal by Division by 10            | 189        |

| Figure 7.9    | Conversion from Binary to Decimal by Decimal Multiplication    | 190        |

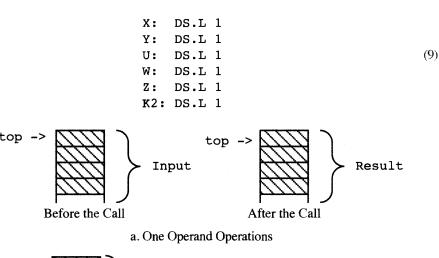

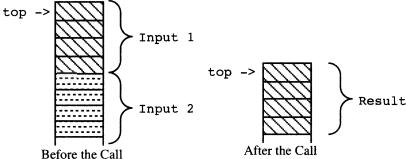

| Figure 7.10   | Passing Parameters on the Stack                                | 192        |

| Figure 7.11   | Stack Movement when Evaluating (8)                             | 193        |

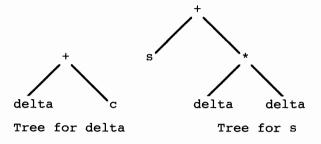

| Figure 7.12   | Finding a Parsing Tree for (5) from the Bottom Up              | 194        |

| Figure 7.13   | Algorithm to Write a Sequence of Subroutine Calls for (5)      | 195        |

| Figure 7.14   |                                                                | 197        |

| •             | 32-Bit Compare Subroutine                                      | 198        |

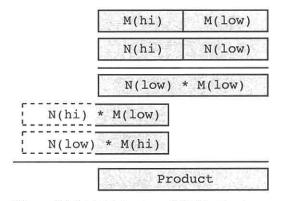

| Figure 7.16   | Multiplication of 32-Bit Numbers                               | 198        |

| Figure 7.17   | 32-Bit by 32-Bit Unsigned Multiply Subroutine                  | 199        |

| Figure 7.18   | 32-Bit by 32-Bit Unsigned Divide Subroutine                    | 199        |

| Figure 7.19   | Push-and-Add Subroutine                                        | 201        |

|               | Procedure for Floating-Point Addition                          | 209        |

| Figure 7.21   | Fuzzy Logic Control System                                     | 211        |

| Figure 7.22   | Membership Functions                                           | 211        |

| Figure 7.23   | A Fuzzy Inference Kernel                                       | 213        |

| Figure 8.1    | Conditional Statements                                         | 226        |

| Figure 8.2    | Case Statements                                                | 227        |

| Figure 8.3    | Loop Statements                                                | 228        |

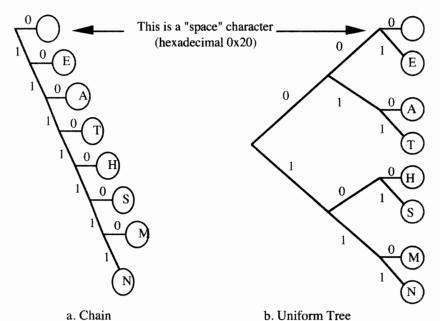

| Figure 8.4    | A Huffman Coding Tree                                          | 233        |

| Figure 8.5    | Other Huffman Codes                                            | 247        |

| List of Figu | res                                                             | XVII |

|--------------|-----------------------------------------------------------------|------|

|              |                                                                 |      |

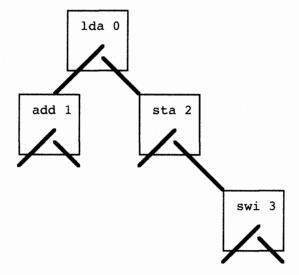

| Figure 9.1   | A Simple Program                                                | 254  |

| Figure 9.2   | A C Program with Local and Global Variables                     | 258  |

| Figure 9.3   | A C Program with Some Operators                                 | 260  |

| Figure 9.4   | A C Program with Incrementing and Decrementing                  | 262  |

| Figure 9.5   | A C Program with ORing, ANDing and Shifting                     | 264  |

| Figure 9.6   | A Program with Boolean Operators                                | 266  |

| Figure 9.7   | A Program with If-Then Expressions                              | 269  |

| Figure 9.8   | Assembly Language for a Decision Tree                           | 270  |

| Figure 9.9   | Alternative Assembly Language for a Case Statement              | 273  |

| Figure 9.10  | For, While, and Do While Loops                                  | 274  |

| Figure 9.11  | Array Manipulation Program                                      | 276  |

| Figure 9.12  | Clearing a Vector with a Do While Loop                          | 277  |

| Figure 9.13  | A Program Setting and Testing a Bit                             | 278  |

| Figure 9.14  | A Subroutine to Raise a Number to a Power                       | 280  |

| Figure 9.15  | Stack for power Procedure                                       | 280  |

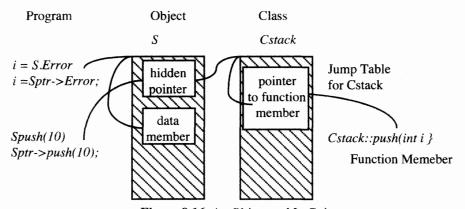

| <b>~</b> .   | An Object and Its Pointers                                      | 281  |

|              |                                                                 |      |

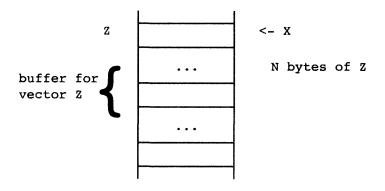

| Figure 10.1  | A Vector Z                                                      | 292  |

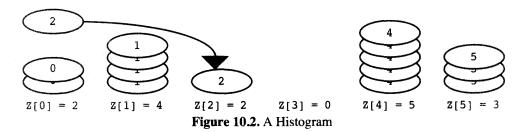

| Figure 10.2  | A Histogram                                                     | 294  |

| Figure 10.3  | An Array                                                        | 295  |

| Figure 10.4  | Subroutine ZTRANS                                               | 297  |

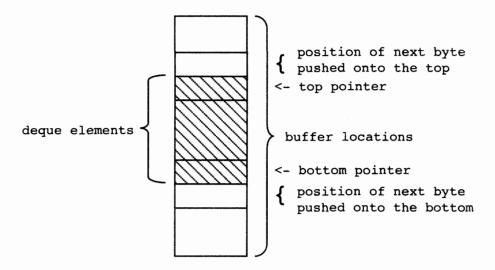

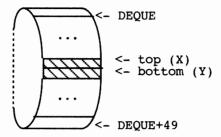

| Figure 10.5  | Deque Data Structure                                            | 301  |

| Figure 10.6  | Buffer for a Deque Wrapped on a Drum                            | 301  |

|              | Subroutines for Pushing and Pulling B from the Top of the Deque | 303  |

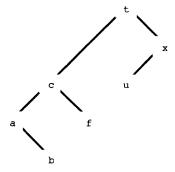

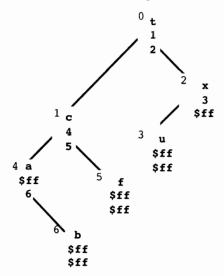

|              | Picture of the Tree Representing the String (12)                | 304  |

| Figure 10.9  | Linked List Representation of the Tree Shown in Figure 10.8     | 305  |

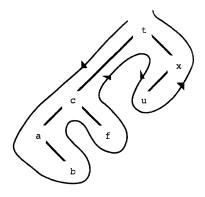

| Figure 10.10 | Path for Scanning the Tree                                      | 306  |

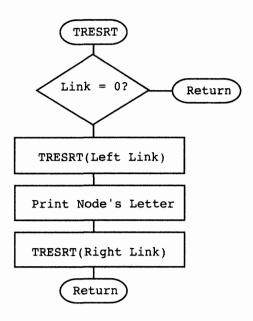

| Figure 10.1  | Flowchart for Scanning Tree                                     | 307  |

| Figure 10.12 | 2 Subroutine SCAN Using Indexes                                 | 308  |

| Figure 10.13 | Linked List Data Structure for SCAN                             | 308  |

| Figure 10.14 | Subroutine SCAN Using Address Pointers                          | 309  |

|              |                                                                 |      |

| Figure 11.1  | Simplified Diagram of a Microcomputer                           | 317  |

|              | A Memory and Its Connection to the MPU                          | 318  |

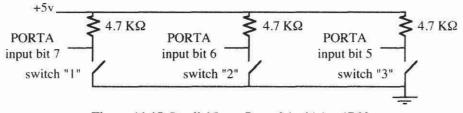

| Figure 11.3  | Some 6812 Parallel I/O Ports                                    | 320  |

| Figure 11.4  | Simple Devices                                                  | 322  |

| Figure 11.5  | A Traffic Light                                                 | 323  |

| Figure 11.6  | Flow Charts for Programmed I/O                                  | 324  |

| Figure 11.7  | The Counter/Timer Subsystem                                     | 325  |

| Figure 11.8  | Status Port                                                     | 328  |

| Figure 11.9  | Interrupt Request Path                                          | 330  |

| Figure 11.10 | D-to-A Converter                                                | 335  |

|              | A-to-D Subsystem of the 'A4 or 'B32                             | 336  |

| Figure 11.12 | 2 Frame Format for UART Signals                                 | 337  |

| Figure 11.13 | 3 6812 Serial Communication Interface                           | 338  |

| Figure 11.14 | Parallel Output Port of the A4 or 'B32                          | 341  |

| Figure 11.15 | Parallel Input Port of the 'A4 or 'B32                          | 341  |

| List of Figures                                             | XIX |

|-------------------------------------------------------------|-----|

| Figure 11.16 Parallel D-to-A Output Port of the 'A4 or 'B32 | 342 |

| Figure 11.17 Johnson Counter Sequence                       | 342 |

| Figure 11.18 Program with Disassembly                       | 344 |

| Figure 11.19 Another Program with Disassembly               | 346 |

| Figure 12.1 A 6811 Dot Product Subroutine                   | 350 |

| Figure 12.2 Registers of the 6808                           | 353 |

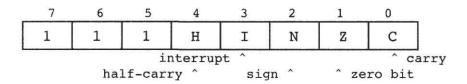

| Figure 12.3 Bits in the 6808 Condition Code Register        | 353 |

| Figure 12.4 A 6808 Dot Product Subroutine                   | 355 |

| Figure 12.5 The Register Set of the 6805                    | 356 |

| Figure 12.6 Bits in the 6805 Condition Code Register        | 356 |

| Figure 12.7 A 6805 Dot Product Subroutine                   | 358 |

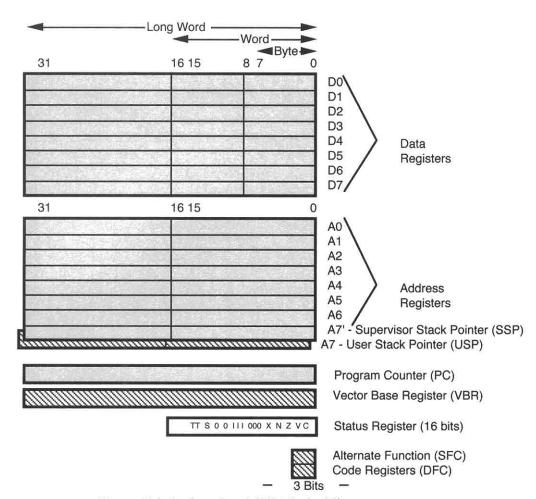

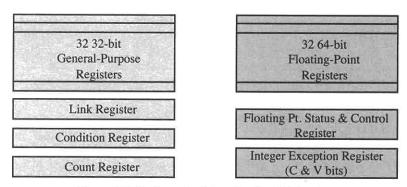

| Figure 12.8 Register Set of 68300 Series Microcomputers     | 359 |

| Figure 12.9 Memory Spaces in the 68300 Series               | 360 |

| Figure 12.10 A 68300 Series Dot Product Subroutine          | 366 |

| Figure 12.11 User Registers for the 500 Series              | 367 |

| Figure 12.12 A 500 Series Dot Product Subroutine            | 369 |

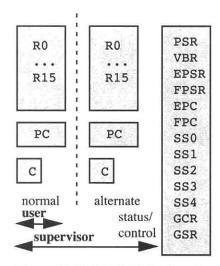

| Figure 12.13 M·CORE Register Set                            | 371 |

| Figure 12.14 An M·CORE Dot Product Subroutine               | 373 |

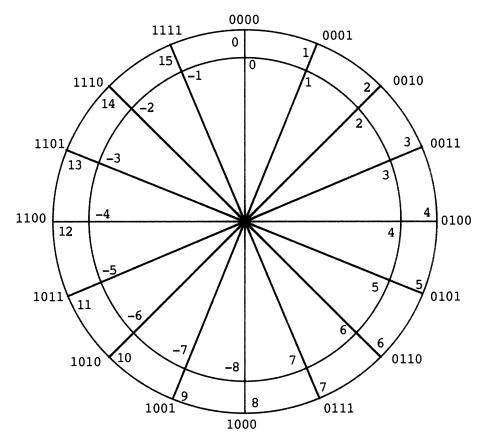

| Figure A1.1 4-Bit Binary Representations                    | 383 |

XX List of Tables

## **List of Tables**

| Table      | Title                                                        | Page |

|------------|--------------------------------------------------------------|------|

| Table 2.1  | Move Instructions Using an Effective Address                 | 29   |

| Table 2.2  | Stack Move Instructions                                      | 30   |

| Table 2.3  | Special Move Instructions                                    | 31   |

| Table 2.4  | Add Instructions Using an Effective Address                  | 34   |

| Table 2.5  | Arithmetic Instructions That Do Not Use an Effective Address | 36   |

| Table 2.6  | Logic Instructions                                           | 39   |

| Table 2.7  | Edit Instructions                                            | 40   |

| Table 2.8  | Conditional Branch Instructions                              | 43   |

| Table 2.9  | Other Control Instructions                                   | 45   |

| Table 2.10 | Special Instructions                                         | 50   |

| Table 4.1  | ASCII Codes                                                  | 87   |

| Table 4.2  | Addressing Modes                                             | 91   |

| Table 4.3  | Assembler Directives                                         | 93   |

| Table 5.1  | S-Record Fields                                              | 122  |

| Table 5.2  | Relocation Directives                                        | 123  |

| Table 5.3  | Conditional Directives                                       | 126  |

| Table 5.4  | Macro Directives                                             | 127  |

| Table 5.5  | Macro Arguments                                              | 128  |

| Table 5.6  | Listing Directives                                           | 130  |

| Table 8.1  | Conventional C Operators Used in Expressions                 | 224  |

| Table 8.2  | Special C Operators                                          | 225  |

| Table 8.3  | Conditional Expression Operators                             | 225  |

| Table 11.1 | Interrupt Vectors in the 6812 'A4                            | 334  |

| Table 12.1 | Instruction Set and Addressing Modes of the 6811             | 351  |

| Table 12.2 | Instruction Set and Addressing Modes of the 6808             | 354  |

| Table 12.3 | Instruction Set and Addressing Modes of the 6805             | 357  |

| Table 12.4 | Addressing Modes for the 68300 Series                        | 361  |

| Table 12.5 | Move and Arithmetic Instructions for the 68300 Series        | 362  |

| Table 12.6 | Other Instructions for the 68300 Series                      | 363  |

| Table 12.7 | Instructions for the 500 Series                              | 368  |

| Table 12.8 | Instructions for the M·CORE Series                           | 372  |

Acknowledgments xxi

### Acknowledgments

The author would like to express his deepest gratitude to everyone who contributed to the development of this book. The students of EE 319K at the University of Texas at Austin during fall 1998 significantly helped correct this book; special thanks are due to Chao Tan, Brett Wisdom, Alex Winbow, Eric Wood, John Prochnow, and Nathan Madino for finding the most errors. This text was prepared and run off using a Macintosh and LaserWriter, running WriteNow. I am pleased to write this description of the Motorola 6812, which is an incredibly powerful component and a vehicle for teaching a considerable range of concepts.

G. J. L.

About the Author

#### **About the Author**

G. Jack Lipovski has taught electrical engineering and computer science at the University of Texas since 1976. He is a computer architect internationally recognized for his design of the pioneering database computer, CASSM, and the parallel computer, TRAC. His expertise in microcomputers is also internationally recognized by his being a past director of Euromicro and an editor of IEEE Micro. Dr. Lipovski has published more than 70 papers, largely in the proceedings of the annual symposium on computer architecture, the IEEE transactions on computers, and the national computer conference. He holds eight patents, generally in the design of logic-in-memory integrated circuits for database and graphics geometry processing. He has authored seven books and edited three. He has served as chairman of the IEEE Computer Society Technical Committee on Computer Architecture, member of the Computer Society Governing Board, and chairman of the Special Interest Group on Computer Architecture of the Association for Computer Machinery. He has been elected Fellow of the IEEE and a Golden Core Member of the IEEE Computer Society. He received his Ph.D. from the University of Illinois, 1969, and has taught at the University of Florida and at the Naval Postgraduate School, where he held the Grace Hopper chair in Computer Science. He has consulted for Harris Semiconductor, designing a microcomputer, and for the Microelectronics and Computer Corporation, studying parallel computers. He founded the company Linden Technology Ltd. and is the chairman of its board. His current interests include parallel computing, database computer architectures, artificial intelligence computer architectures, and microcomputers.

# Basic Computer Structure and the 6812

Computers, and microcomputers in particular, are among the most useful tools that humans have developed. They are not the news media's mysterious half-human forces implied by "The computer will decide . . ." or "It was a computer error!" No, computers are actually like levers; as a lever amplifies what the human arm can do, so the computer amplifies what the human brain can do. Good commands are amplified, and the computer is a great tool, but bad commands are likewise amplified, and good commands incorrectly programmed are also amplified. "To err is human, but to really foul things up, you need a computer." You have to study and exercise this tool to make it useful; that is the purpose of this book. The computer also has to be used with insight and consideration for its effects on society, but that will not be studied in this book.

We shall study the computer as an engineer studies any tool—we begin by finding out just how it ticks. We make our discussion concrete using the well-designed Motorola 6812 microcomputer, as a means of teaching the operations of computers in general. In this chapter we introduce basic computer structure. We discuss memory, how memory words are read to tell the microcomputer what to do, and how these words are written and read to save the microcomputer's data. Finally, we describe a small but useful subset of 6812 instructions to show how a computer reads and carries out an instruction and a program, to introduce the idea of programming.

After reading this chapter, you should be able to approach a typical instruction, to be introduced in the next two chapters, with an understanding about what the mnemonic, the machine code, and a sequence of memory reads and writes may mean for that instruction. This chapter then provides background for the discussion of instructions that we will present in the next two chapters.

#### 1.1 Basic Computer Structure

What is a microcomputer, and how does it execute the instructions that a programmer writes for it? This question is explored now at a level of abstraction that will be adequate for this text. We do know that many readers will object to one aspect of the following

discussion, and we want to answer that objection a priori, so that those readers will not miss the point. We will introduce a seemingly large number of terms. Don't miss the objective: We are really introducing concepts. The reader should think about the concepts rather than memorize definitions. Like your physics text, this text has to use terms in a fairly precise way to avoid ambiguity. Your physics text, you may recall, used the word "work" in a very precise way, as the product of force times distance, which is a bit different from the conversational use of the word "work" as used in the expression, "He's doing a lot of work." We will use terms such as "read" and "fetch" in a similar way. When defined, they will be written in *italics* and will be listed in the index. We ask you to learn the term and its meaning even though you do not have to memorize the wording of the definition. But take heart, because although we do have a few concepts that have to be learned, and we have to learn the terms for those concepts, we do not have many formulas or equations to deal with. Accept our challenge to understand these terms; then you will enjoy the latter discussions even more than if you muddle through this section without thinking about the terminology.

You probably know what microcomputers and computers are, to some degree, but let us discuss the term "computer" so that if you get into an argument about whether a hand calculator is a computer, you can respond knowledgeably.

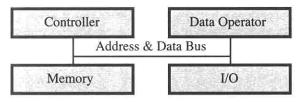

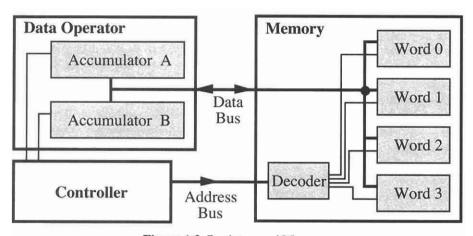

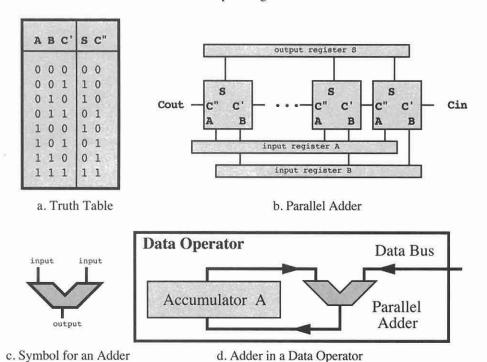

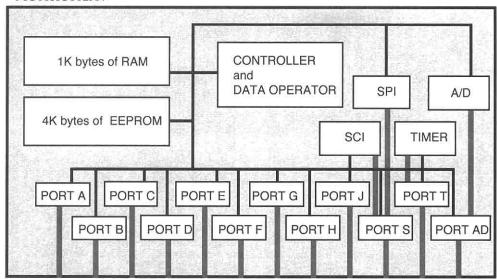

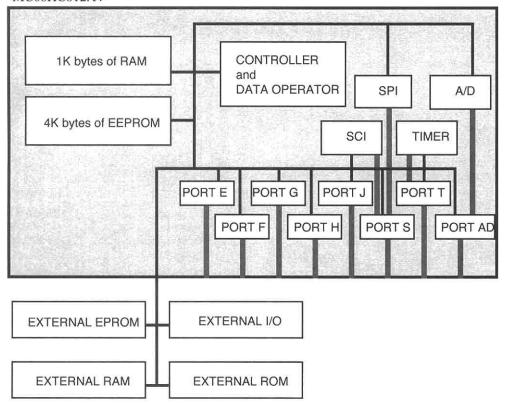

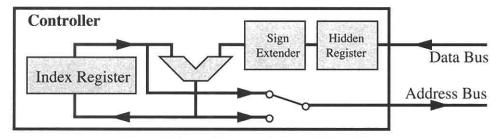

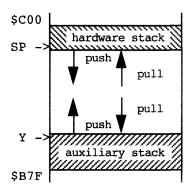

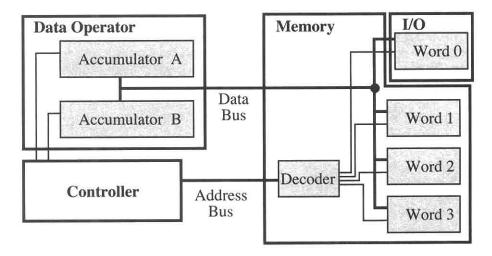

A microcomputer is a kind of computer or, more accurately, a kind of von Neumann computer, named after the scientific giant of our century who invented it. All von Neumann computers have four components: memory, controller, data operator (sometimes called an arithmetic-logic unit), and input-output (I/O), which are connected by an address and data bus. A simplified diagram of a computer is shown in Figure 1.1. Briefly, the memory stores both the data and the program, and the inputoutput provides the communication with the outside world. In a conventional personal computer system input-output is done through peripherals such as CRTs, keyboards, scanners, printers, modems, and so on. In typical microcontroller applications the inputoutput system provides the necessary connections, or interfacing, to the device, of which the microcontroller is a component, such as an automobile, kitchen appliance, toy, or laboratory instrument. The data operator performs arithmetic and logical operations on data, such as addition, ANDing, and so on. The controller controls the flow of information between the components by means of control lines (which are not shown in Figure 1.1), directing what computation is to be done. The input/output, controller, and data operator may themselves contain a small amount of memory in registers.

A microcomputer is a computer that is implemented using low-cost integrated circuits (ICs) and is therefore cheap enough to be used in an incredible range of applications where a large computer would be infeasible. For the purposes of this book, if the data operator and the controller are together on a single IC, but other ICs are needed to complete the computer, that IC is called a *microprocessor*; the computer that uses a

Figure 1.1. Simplified Computer Structure

microprocessor is called a *microcomputer*; and, if a complete computer is on a single integrated circuit, that integrated circuit is called a *single-chip microcontroller*.

Some aspects of microcomputers apply to all computers. We will often discuss an aspect of the computer and, of course, that aspect applies to microcontrollers, on which we are concentrating. The microcomputer's, or microcontroller's, controller and data operator is abbreviated MPU (microprocessor unit). The abbreviation CPU (central processor unit) is often used to denote the controller and data operator, but that term leads subtly to the idea that the CPU is central and most important; but this is misleading, especially when a computer system has many MPUs, none of which is "central."

We now look more closely at the memory and the MPU. We can think of the memory as a large number of cells, each able to store a 0 or a 1—that is, a binary digit or one bit of memory. The bits are grouped together in units called *bytes*, which consist of 8 bits. Within a particular byte the bits are labeled b7, . . ., b0 as shown.

| b7   | b6 | b5 | b4 | b3 | b2 | b1 | ь0 |

|------|----|----|----|----|----|----|----|

| Byte |    |    |    |    |    |    |    |

The right-hand bits are called lower-order or least significant, and the left-hand bits are called higher-order or most significant. There is nothing sacred about this labeling, and, in fact, many computer manufacturers reverse it. A word in memory is the number of bits that are typically read or written as a whole. In small microcomputers, a word is one byte, so that the terms "word" and "byte" are often used interchangeably. In this text, the 6812 can read an 8-bit or a 16-bit word, which is two bytes. In a 16-bit word, bits are numbered from 15 (on the left) to 0 (on the right). In the memory, each byte has an address between 0 and  $2^N - 1$ , where N is the total number of address bits. In the 6812, N is essentially 16, so each address between 0 and 65,535 is described by its 16-bit binary representation (see Appendix 1), although some 6812 versions can extend this range.

The MPU controls the memory by means of a clock and a read/write line, and communicates to it by an address bus and a data bus, shown in Figure 1.1. A line or wire carries one bit of information at each instance of time by the level of voltage on it. Each line can carry a true (1) or a false (0) value. A bus is a collection of lines that can move a word or an address in parallel, so that one bit of a word or address is on one line of the bus. The data bus moves an 8-bit or 16-bit word to or from memory and from or to the MPU, and the address bus moves a 16-bit address from the MPU to the memory. A clock is a signal that is alternately a 0 and 1 (a square wave). A clock cycle is the time interval from when the clock just becomes 0 until the next time it just becomes 0, and the clock rate, or clock frequency, is the reciprocal of the clock cycle time. Contemporary 6812 microcontrollers essentially use an 8 MHz clock.

In one clock cycle, the MPU can *read* a word from the memory by putting an address on the address bus and making the *read/write line* 1 for the cycle and then picking up the word on the data bus at the end of the cycle. It can also *write* a word into the memory in one clock cycle by putting the address on the address bus and putting the word on the data bus and making the read/write line 0 for the cycle. A read or a write to memory is also called an *access* to memory.

We can enlarge our description of how the memory works. Assume that we want to get the contents of a particular word or byte from memory, that is, read a word from memory. The MPU first puts a 1 for read on the read/write line and then puts the address of the desired word or byte on the address bus throughout the duration of a clock cycle. The memory is designed so that, at the end of the clock cycle, the desired word is put on the data bus. The MPU then places a copy of the contents of the word or byte on the data bus into some register inside the MPU as required by the instruction that it is executing. This is done without changing the contents in memory of the word or byte addressed.

To write a word into memory, the address of the word is put on the address bus, the word is put on the data bus, and the read/write line has 0 (to indicate a write) for a full clock cycle. The memory is designed to store the word at that address at the end of the clock cycle. After the word is stored at the given address, the MPU may still retain in one of its registers a copy of the word that has just been written.

The MPU can read or write an 8-bit or a 16-bit word in memory in one clock cycle. Such a memory is usually called random access memory or RAM because each byte is equally accessible or can be selected at random without changing the time of the access. With microcomputer applications, it is not unusual to have part of the memory bytes in ROM (read only memory). A ROM is capable of a read operation but not a write operation; its words are written when it is made at the factory and are retained even when the power is turned off. If the data in a RAM are lost when power is turned off, the RAM is termed volatile; otherwise, it is termed nonvolatile. RAM memories are essentially volatile. The term RAM is also used almost universally to imply memories that you can read and write in, even though ROM memories can be randomly accessed with a read operation. The part of memory that is in ROM is typically used to store a program for a microcomputer that only executes one program. For example, the microcontroller used in an automobile would be running the same program every time it is used, so that the part of the memory that is used for storing the program is in ROM.

#### 1.2 The Instruction

We now examine the notion of an *instruction*, which is an indivisible operation performed by the MPU. It can be described statically as a collection of bits stored in memory or as a line of a program or, dynamically, as a sequence of actions by the controller. In this discussion we begin with a simplified dynamic view of the instruction and then develop a static view. Examples are offered to combine these views to explain the static aspects of the operation code, addressing mode, machine code, and mnemonics. We conclude with an expanded view of the dynamic aspects of the instruction cycle.

The controller will send commands to memory to read or write and will send commands to all other parts of the computer to effectively carry out the intentions of the programmer. The specification of what the control unit is to do is contained in a program, a sequence of instructions stored, for the most part, in consecutive bytes of memory. To execute the program, the MPU controller repeatedly executes the instruction cycle (or fetch/execute cycle):

1. Fetch (read) the next instruction from memory. 2. Execute the instruction.

1.2 The Instruction 5

As we shall see with the 6812 MPU, reading an instruction from memory will require that one or more bytes be read from memory. To execute the instruction, some bytes may also be read or written. These two activities, read and execute, seem to be read or write operations with the memory but are quite different to the MPU, and we use different terms for them. To *fetch* means to read a word from memory to be used as an instruction in the controller. The first step in the cycle shown previously is the *fetch* phase. To recall means to read a word into the MPU that is not part of the instruction. The recall and write operations are done in the second step of the instruction, which is called the execute phase. Thus, when we talk about fetching a word, you can be sure that we are talking about reading the instruction, or part of the instruction. We will not use "fetch" to describe an operation of reading data to be input to the data operator.

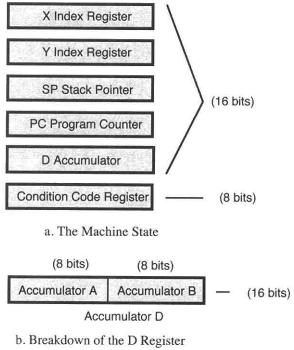

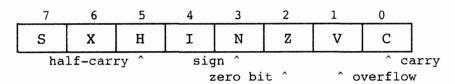

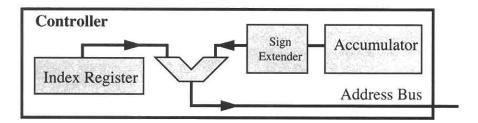

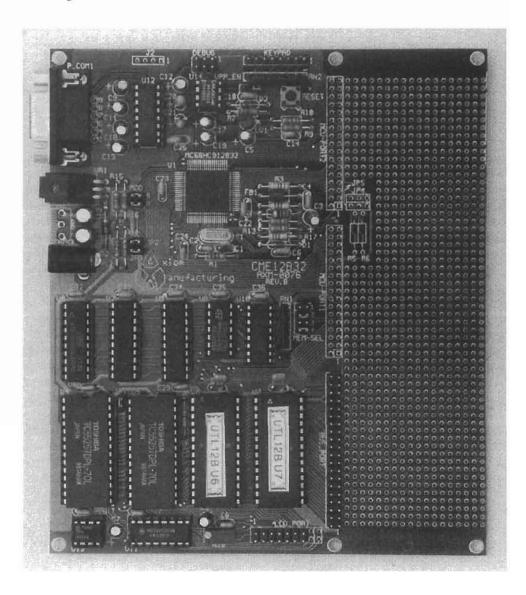

The 6812's registers are shown in Figure 1.2, where the top five registers hold 16 bits and the condition code register holds 8 bits. The 16-bit D register is composed of two 8-bit registers A and B; D, A, and B are called accumulators because arithmetic operations can be done with their contents with the results placed back in the registers to accumulate the result. This accumulating aspect of registers D, A, and B will be assumed to be understood so that we often refer to (register) "D," "A," or "B" rather than "accumulator D," "accumulator A," or "accumulator B." The registers A and B are always the left and right halves of register D; if you put \$12 in register A and \$34 in register B then read register D, it has \$1234. Similarly, if you put \$5678 in register D, then reading register A gives \$56 and reading register B gives \$78. Registers X and Y are

Figure 1.2. Registers in the 6812

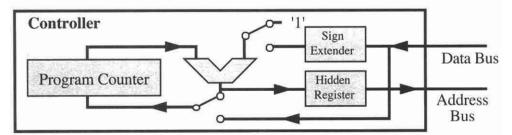

index registers, and SP is a stack pointer; they are used in address calculations. The program counter, PC, is used to fetch the instruction. It is called a counter because it normally increments each time it is used. The condition code register (CC) has bits that are used to indicate results of tests that can be used in conditional branch instructions.

At the beginning of the instruction cycle it is assumed that the program counter contains the address of the first byte of the instruction. As each byte of the instruction is fetched, the PC is incremented by 1, so that the PC always has the address of the next byte of the instruction to be read from memory. When the instruction cycle is completed, the PC then automatically contains the address of the first byte of the next instruction.

We now look at the instruction statically as one or more memory bytes or as a line of a program. This discussion will introduce new concepts, but we have tried to keep the number down so that the examples can be discussed without your having too many terms to deal with. The examples will help to clarify the concepts that we introduce below.

Each instruction in a microcomputer carries out an operation. The types of operations provided by a von Neumann computer can be categorized as follows:

Move.

Arithmetic.

Logical.

Edit.

Control.

Input/output.

At this time, we are interested in how instructions are stored in memory as part of a program and how they are executed by the 6812.

After the instruction is fetched, the execute phase of the fetch execute cycle will often use an address in memory for the input data of the operation or for the location of the result of the operation. This location is called the *effective address*. The Motorola 6812, like most microcomputers, is a *one-address computer* because each instruction can specify at most one effective address in memory. For instance, if an instruction were to move a word from location 100 in memory into register A, then 100 is the effective address. This effective address is generally determined by some bits in the instruction. The *addressing mode* specifies how the effective address is to be determined, and there are binary numbers in the instruction that are used to determine the address. The effective address is calculated at the beginning of the execute phase, just after the instruction is fetched and before any of the operations actually take place to execute the instruction.

An instruction in the 6812 is stored in memory as one or more bytes. The first, and possibly only, byte of the instruction is generally the operation code byte. The operation code byte contains the operation code (opcode, for short), which specifies the operation to be carried out and the specification of the addressing mode. The remaining bytes of the instruction, if any, specify the effective address according to the given addressing mode. The bytes representing the instruction can be represented as a sequence of ones and zeros, that is, a binary number. The trouble with this is that it is hard to remember and to check an 8-bit or longer string of ones and zeros. To make it easier, we can represent the bit pattern as a hexadecimal number. A hexadecimal number will be prefixed by a dollar sign (\$) to distinguish it from a decimal number. (For example, 193 = \$C1. If you are unfamiliar with hexadecimal numbers, see Appendix 1.) When the opcode, addressing modes, and constants used to determine the address are represented either as binary or hexadecimal numbers, we call this representation the machine code because it is the actual format used to store the instruction in the machine (microcomputer), and this format is used by the machine to determine what is to be done.

1.2 The Instruction 7

Machine code is quite useful for making small changes in a program that is being run and corrected or *debugged*. However, writing even a moderately long program in machine code is a punishment that should be reserved for the fifth level of Dante's inferno. In Chapter 4 we discuss how text produced by an editor is converted by an assembler to the machine code stored in the computer's memory. The text input to the assembler is called source code. In a line of source code, to make remembering the instructions easier, a three- or four-character mnemonic is used to describe the operation, and its addressing information may be given as a hexadecimal or a decimal number. A line of source code, consisting of mnemonics and addressing information, can be converted by hand into their hexadecimal machine code equivalents using Motorola's CPU12 Reference Guide (you can order it from Motorola by using reference number CPU12RG/D). In the first three chapters, we want to avoid using the assembler, to see clearly just how the computer ticks. We will hand-convert mnemonics and addressing information to hexadecimal machine code and work with hexadecimal machine code.

We now look at a load immediate instruction in detail, to introduce concepts about instructions in general. The load instruction will move a byte into an accumulator, either A or B. Its simplest addressing mode is called *immediate*. For instance, to put a specific number, say \$2F, in accumulator A, execute the instruction whose source code line is

#### LDAA #\$2F

where the symbol "#" denotes immediate addressing and the symbol "\$" is used to indicate that the number that follows is in hexadecimal. This instruction is stored in memory as the two consecutive bytes:

| \$8  | 6 |

|------|---|

| \$21 | F |

(Look in CPU12 Reference Guide, Instruction Set Summary, for the mnemonic LDAA and, under it, find \$86 in under the Machine Coding column, in the row beginning LDAA #opr8i, which also has the addressing mode IMM for immediate addressing.)

Looking dynamically at an instruction, an operation (e.g., add, subtract, load, clear, etc.) may be carried out with inputs (or *operands*) and may produce a result. The instruction is executed in the instruction cycle as follows.

- 1. Fetch the first byte of the instruction from memory.

- 2. Increment the PC by one.

- 3. Decode the opcode that was fetched in step 1.

- 4. Repeat steps 1 and 2 to fetch all bytes of the instruction.

- 5. Calculate the effective address to access memory, if needed.

- 6. Recall the operand from memory, if needed.

- 7. Execute the instruction, which may include writing the result into memory.

The controller fetches the first byte, \$86. The program counter is incremented. The controller decodes \$86. The controller fetches the second byte, \$2F, putting it into accumulator A. The program counter is incremented. After this instruction is executed, another instruction is fetched and executed.

#### 1.3 A Few Instructions and Some Simple Programs

Now that we have examined the instruction from static and dynamic points of view, we will look at some simple programs. The machine code for these programs will be described explicitly so that you can try out these programs on a real 6812 and see how they work, or at least so that you can clearly visualize this experience. The art of determining which instructions have to be put where is introduced together with a discussion of the bits in the condition code register. We will discuss what we consider to be a good program versus a bad program, and we will discuss what is going to be in Chapters 2 and 3. We will also introduce an alternative to the immediate addressing mode using the load instruction. Then we bring in the store, add, software interrupt, and add with carry instructions to make the programs more interesting as we explain the notions of programming in general.

We first consider some variations of the load instruction to illustrate different addressing modes and representations of instructions. We may want to put another number into register A. Had we wanted to put \$3E into A rather than \$2F, only the second byte of the instruction would be changed, with \$3E replacing \$2F. The same instruction as

LDAA #\$3E

could also be written using a decimal number as the immediate operand: for example,

LDAA #62

Either line of source code would be converted to machine code as follows:

\$86 \$3E